# UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

JOÃO MARCELO SILVA SOUZA

## SISTEMA DIGITAL DE SELEÇÃO *ONLINE* DE EVENTOS PARA O DETECTOR NEUTRINOS ANGRA

SALVADOR 2016

# UNIVERSIDADE FEDERAL DA BAHIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

## JOÃO MARCELO SILVA SOUZA

## SISTEMA DIGITAL DE SELEÇÃO *ONLINE* DE EVENTOS PARA O DETECTOR NEUTRINOS ANGRA

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal da Bahia como parte dos requisitos necessários para obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Eduardo Furtado de Simas Filho.

Co-Orientador: Paulo Cesar Machado de Abreu Farias.

Área de Concentração: Processamento Digital de Sinais. Linha de Pesquisa: Sistemas Computacionais e Robótica.

> SALVADOR - BA - BRASIL DEZEMBRO 2016

Souza, João Marcelo Silva

Sistema digital de seleção online de eventos para o detector Neutrinos Angra / João Marcelo Silva Souza. --Salvador, 2016. 91 f. : il

Orientador: Eduardo Furtado de Simas Filho. Coorientador: Paulo Cesar Machado de Abreu Farias. Dissertação (Mestrado - Programa de Pós-Graduação em Engenharia Elétrica) -- Universidade Federal da Bahia, Escola Politécnica, 2016.

1. Sistemas de Trigger. 2. Sistema de Aquisição. 3. Física de Altas Energias. 4. Detector de Neutrinos. I. Filho, Eduardo Furtado de Simas. II. Farias, Paulo Cesar Machado de Abreu. III. Título.

## JOÃO MARCELO SILVA SOUZA

## Sistema Digital de Seleção *Online* de Eventos para o Detector Neutrinos Angra

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica, Escola Politécnica, Universidade Federal da Bahia - UFBA, como requisito parcial para obtenção do grau de Mestre em Engenharia Elétrica.

Aprovada em 19 de dezembro de 2016

Prof. Dr. Eduardo Furtado de Simas Filho

Orientador (UFBA)

Prof. Dr. Paulo César Machado de Abreu Farias

Co-Orientador (UFBA)

Prof. Dr. Luciano Manhães de Andrade Filho

Avaliador Externo (UFJF)

Prof. Dr. Wagner Luiz Alves de Oliveira

Avaljador Interno

Prof. Dr. Antônio Carlos Lopes Fernandes Júnior

Avaliador Interno

"Quem sabe, sabe!

Mas ninguém nasceu sabendo,

a gente vai vivendo é para aprender."

(Quininho de Valente)

## **AGRADECIMENTOS**

Primeiramente agradeço a Deus e a meus pais por todas as oportunidades e por estarem sempre comigo.

Agradeço a minha família pelo conforto, incentivo e forças para alcançar novas conquistas.

Agradeço a meu orientador professor Dr. Eduardo Furtado de Simas Filho pelo apoio na pesquisa, orientação e incentivo.

Agradeço também a Colaboração Neutrinos Angra por todo o suporte na construção do trabalho, bem como toda a equipe do CBPF.

Agradeço aos colegas da *Design House* do SENAI CIMATEC por propiciar o ambiente de inovação em projetos de circuitos integrados e FPGA, que contribuíram para o desenvolvimento deste trabalho.

A FAPESB, CNPQ, FINEP e FAPERJ por financiar esta pesquisa e o detector Neutrinos Angra.

E a todos da UFBA que contribuíram direta e indiretamente para a realização deste trabalho, muito obrigado!

## RESUMO

Este trabalho apresenta o primeiro estágio de seleção *online* de eventos (*trigger*) do detector Neutrinos Angra, o qual foi projetado para medir o fluxo de antineutrinos emitidos pelo reator nuclear Angra II, localizado no estado do Rio de Janeiro, Brasil. Atualmente, o detector está instalado no Centro Brasileiro de Pesquisas Físicas (CBPF), onde vem sendo realizados testes funcionais e procedimentos de calibração. O primeiro nível de *trigger* foi desenvolvido para dispositivos FPGA e inclui módulos adicionais para configuração remota e aquisição de dados. A arquitetura e testes de desempenho são apresentados. Os resultados experimentais foram obtidos utilizando-se como partículas alvo os múons cósmicos, visto que a taxa de antineutrinos no CBPF é muito baixa para ser detectada. Os demais resultados foram obtidos a partir de simulações, *testbenches* e testes em laboratório. A partir deste trabalho foi possível realizar a integração dos sistemas já desenvolvidos previamente para o detector, realizar aquisição do comportamento dos sinais no que tange a comprimentos e frequências, bem como viabilizou a aquisição pela primeira vez de sinais para diferentes valores de *threshold*.

**Palavras-chave** - Sistemas de Trigger, Sistema de Aquisição, Física de Altas Energias, Detector de Neutrinos.

## **ABSTRACT**

This work presents the first stage of the online selection of events (trigger) of the Neutrinos Angra detector, which has been designed to measure the antineutrino flux originated from the Angra II nuclear reactor located in the state of Rio de Janeiro, Brazil. The detector is currently installed in the Brazilian Center for Physics Research (CBPF), where functional tests and calibration procedures are being carried out. The first-level trigger system has been developed for FPGA devices and includes additional modules for remote configuration and data acquisition. The architecture and performance tests are presented. The results were obtained by using as target particles the cosmic muons, since the antineutrinos rate at CBPF is too low to be detected. The other results were obtained from simulations, testbenches and laboratory tests. From this work was possible to perform the integration of the systems previously developed to the detector, to perform signal acquisition and verify the behavior of the signals in reference of the lengths and frequencies, as well as, this work enabled the signals aquisition for the first time of different threshold values.

Keywords - Trigger Systems, Data Acquisition, High Energy Physics, Neutrinos Detector.

## **LISTA DE FIGURAS**

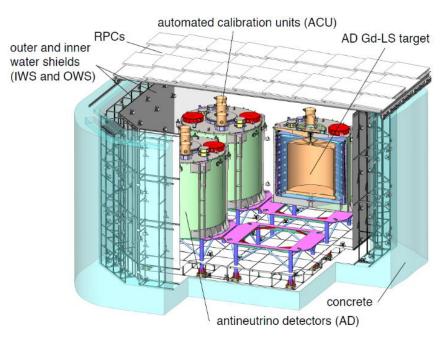

| Figura 1 - Layout do detector padrão de antineutrinos do Daya Bay [21]              | 9  |

|-------------------------------------------------------------------------------------|----|

| Figura 2 - Fotografia de modelos de <i>Photomultiplier Tubes</i> (PMT) [24]         | 10 |

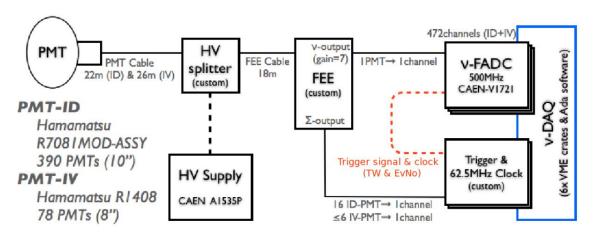

| Figura 3 - Esquemático da cadeia de aquisição do detector Double Chooz [4]          | 10 |

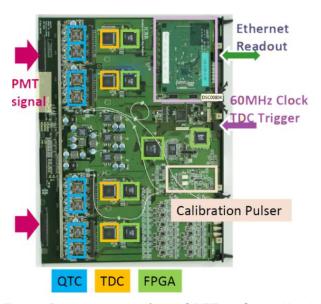

| Figura 4 - Fotografia da placa eletrônica de front-end do detector Borexino [18]    | 11 |

| Figura 5 - Fotografia da placa eletrônica QBEE do Super-Kamiokande [9]              | 11 |

| Figura 6 - Topologia Hierárquica de Trigger de HEP [10]                             | 12 |

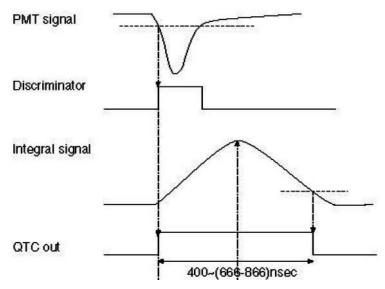

| Figura 7 - Diagrama de tempo do QTC do detector do Super-K [9]                      | 14 |

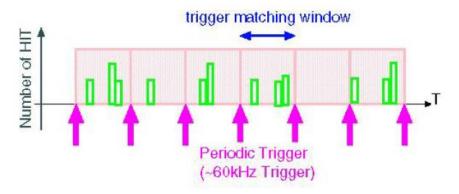

| Figura 8 - Trigger periódico e janela de trigger do experimento Super-K [9]         | 14 |

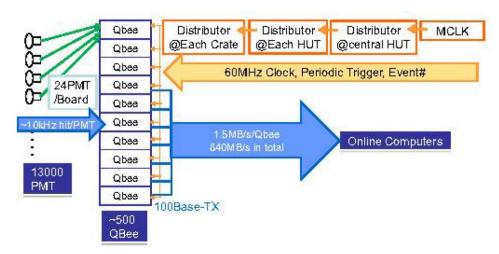

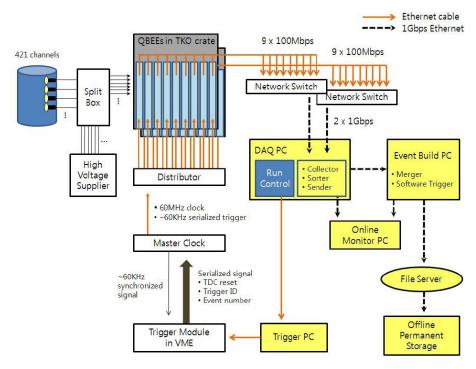

| Figura 9 - Diagrama do Sistema de DAQ com o módulo de <i>clock</i> principal [9]    | 15 |

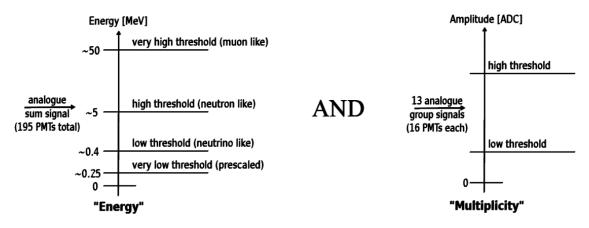

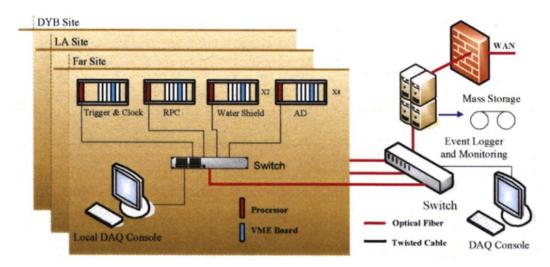

| Figura 10 - Esquemático do sistema de decisão de trigger [4]                        | 16 |

| Figura 11 - Diagrama de blocos da Trigger Board (TB) [4]                            | 17 |

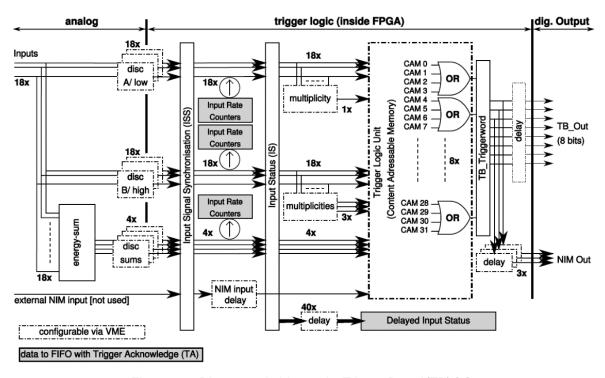

| Figura 12 - Diagrama de funcionamento do circuito ISS [4]                           | 17 |

| Figura 13 - Diagrama de blocos do sistema de aquisição do detector Daya Bay         | 18 |

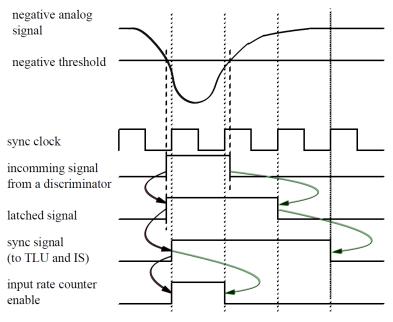

| Figura 14 - Arquitetura base de trigger do detector Borexino [18]                   | 19 |

| Figura 15 - Diagrama do sistema de DAQ e trigger do detector RENO [22]              | 21 |

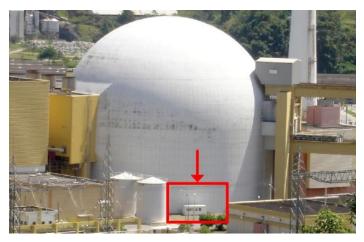

| Figura 16 - Container do detector de neutrinos na usina nuclear de Angra II [17]    | 22 |

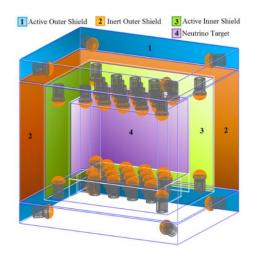

| Figura 17 - Módulos do Experimento Neutrinos Angra [5]                              | 23 |

| Figura 18 - Disposição das PMTs do detector Neutrinos Angra [3]                     | 23 |

| Figura 19 - Placa eletrônica do NDAQ do Neutrinos Angra [12]                        | 24 |

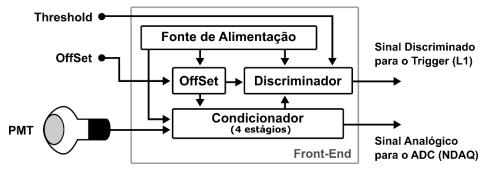

| Figura 20 - Diagrama de blocos do front-end [27].                                   | 24 |

| Figura 21 - Esquemático do circuito de amplificação e filtragem do front-end [28]   | 25 |

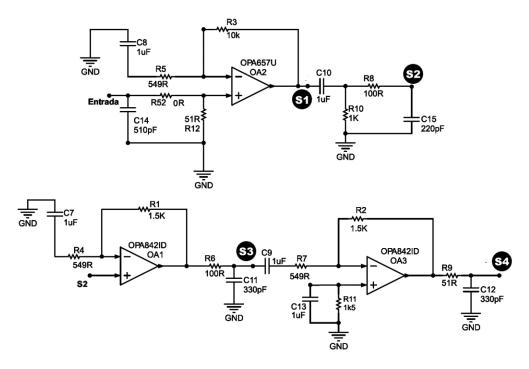

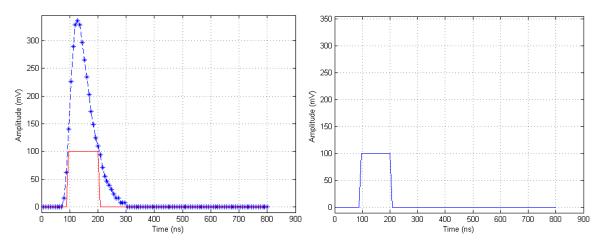

| Figura 22 - Sinal das PMTs e respectivos estágios do front-end [27]                 | 25 |

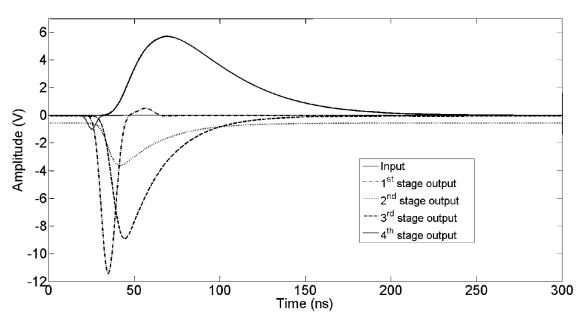

| Figura 23 - Formato dos sinais de saída do front-end.                               | 26 |

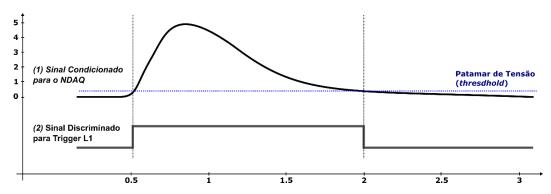

| Figura 24 - Fotografia da placa eletrônica de front-end                             | 26 |

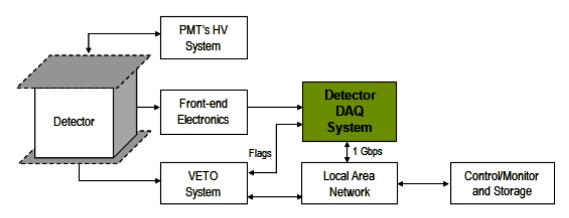

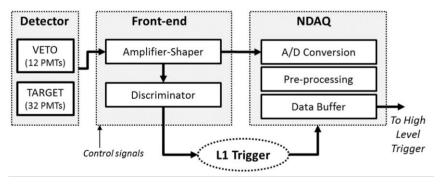

| Figura 25 - Diagrama base dos PMTs, front-end, NDAQ e trigger [3]                   | 27 |

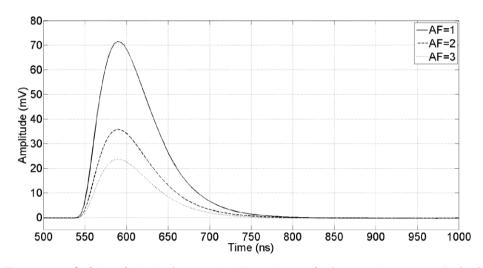

| Figura 26 - Saída média do front-end utilizando os três fatores de atenuação [29]   | 27 |

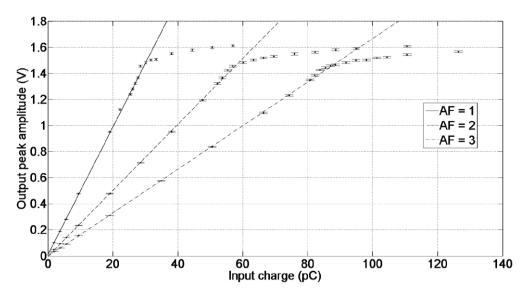

| Figura 27 - Pico de amplitude de saída versus carga de entrada [29]                 | 28 |

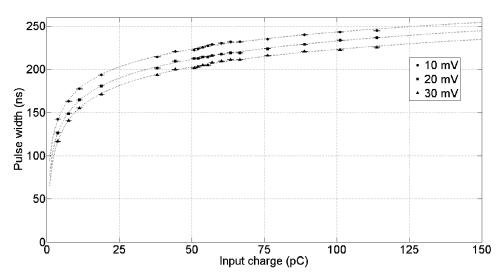

| Figura 28 - Largura do pulso versos carga de entrada para AF = 1 [29]               | 29 |

| Figura 29 - Diagrama do fluxo base das fases de desenvolvimento de ASICs [30] [31]. | 30 |

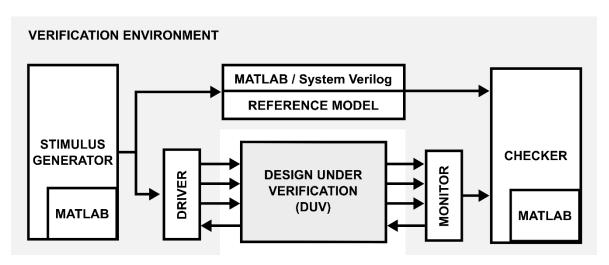

| Figura 30 - Ambiente de verificação do projeto [34] [33].                           | 32 |

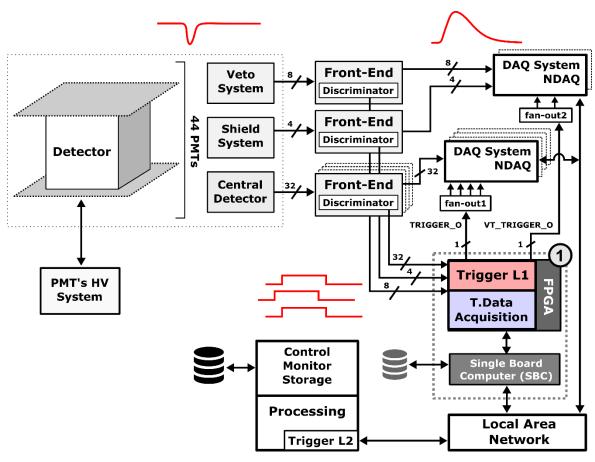

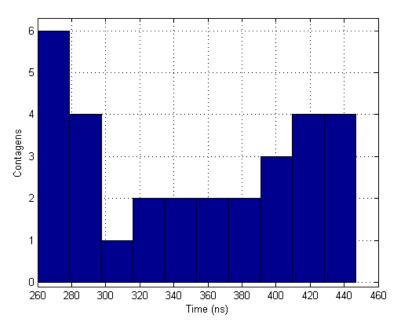

| Figura 31 - Visão geral do sistema de trigger (Item 1) no detector Neutrinos Angra  | 34 |

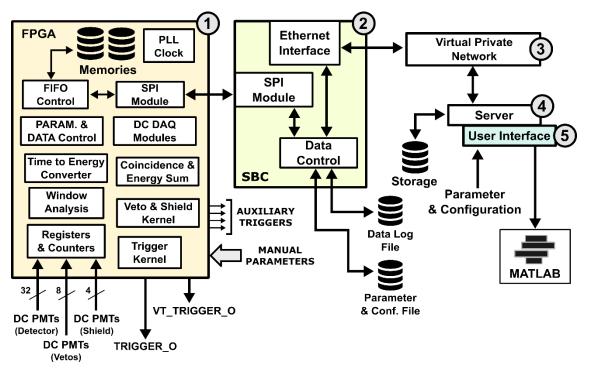

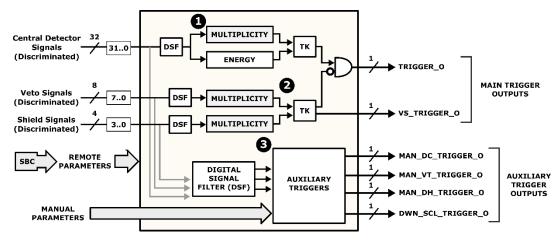

| Figura 32 - Diagrama de blocos macro dos sistemas do projeto                        | 36 |

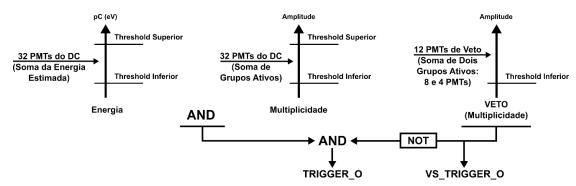

| Figura 33 - Lógica macro de funcionamento dos sistemas de trigger                   | 38 |

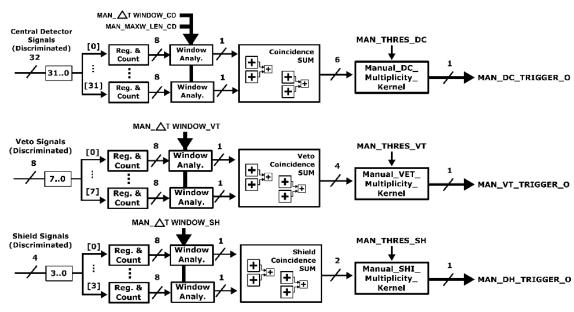

| Figura 34 - Diagrama simplificado dos módulos de <i>trigger</i>                       | 39     |

|---------------------------------------------------------------------------------------|--------|

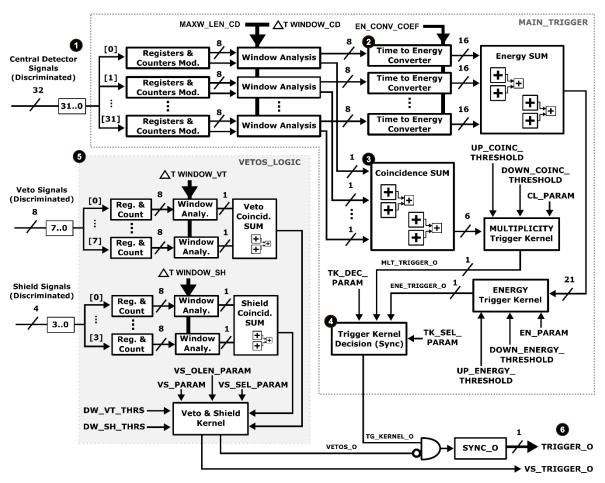

| Figura 35 - Diagrama da arquitetura geral do sistema de trigger.                      | 40     |

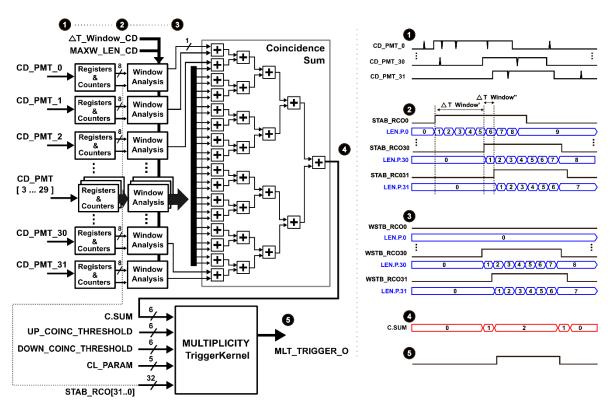

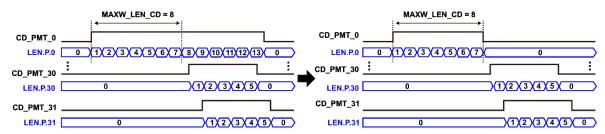

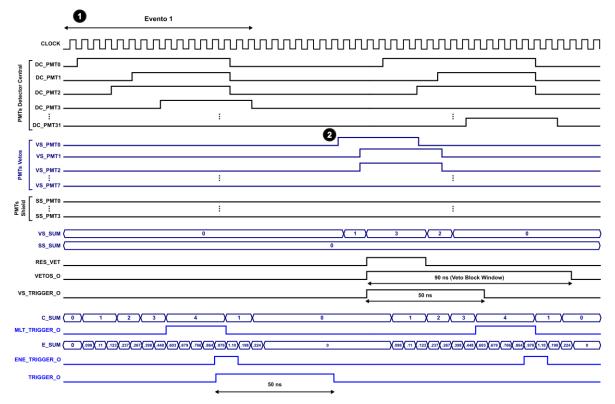

| Figura 36 - Diagrama de sinais dos módulos do <i>trigger</i> por multiplicidade       | 42     |

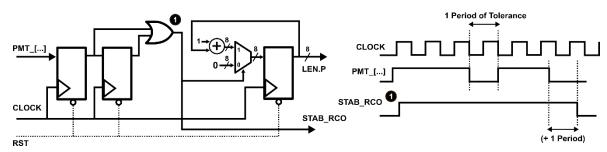

| Figura 37 - Ilustração do funcionamento do módulo Registers & Counters                | 43     |

| Figura 38 - Filtragem de sinal com duração maior que o limite                         | 44     |

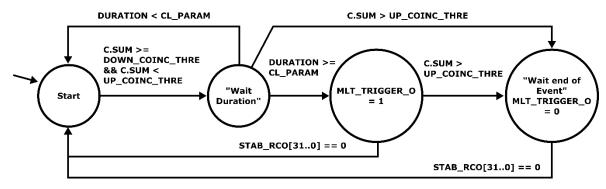

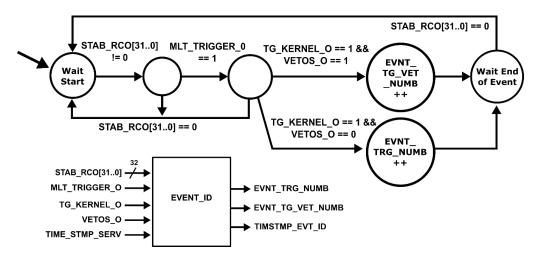

| Figura 39 - Máquina de estados do Multiplicity Trigger Kernel                         | 44     |

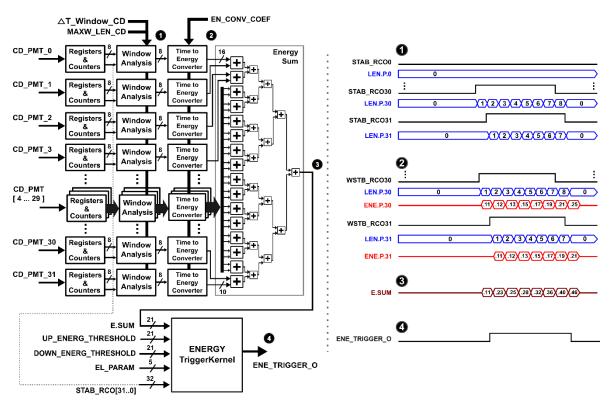

| Figura 40 - Diagrama de sinais dos módulos do <i>trigger</i> por energia              | 45     |

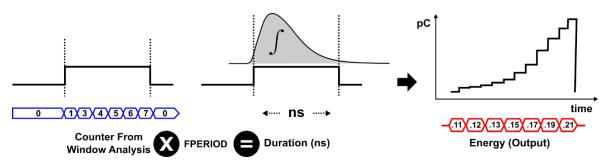

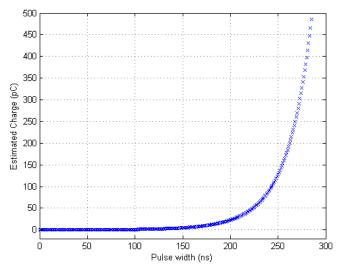

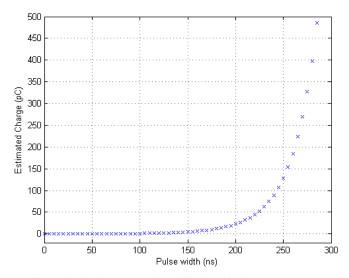

| Figura 41 - Conversão de largura do pulso (ns) para energia (pC)                      | 46     |

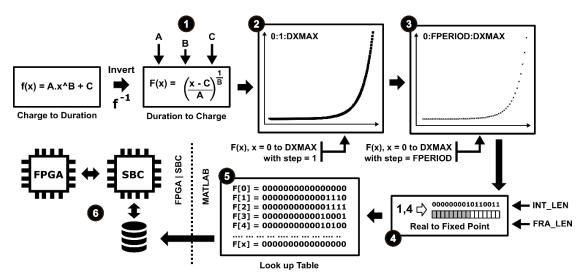

| Figura 42 - Etapas de geração dos dados de conversão de duração para energia          | 47     |

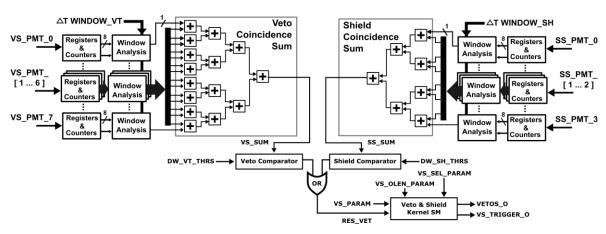

| Figura 43 - Lógica de funcionamento dos vetos e shield                                | 48     |

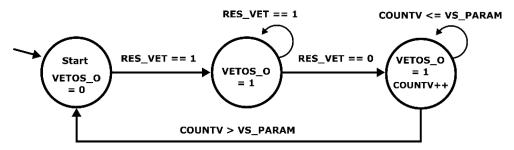

| Figura 44 - Máquina de estados de propagação de sinal de veto                         | 49     |

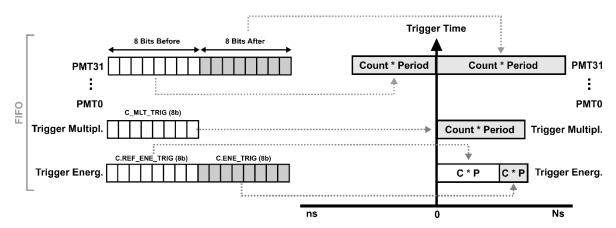

| Figura 45 - Diagrama de sinais e parâmetros dos sistemas de <i>trigger</i> auxiliares | 49     |

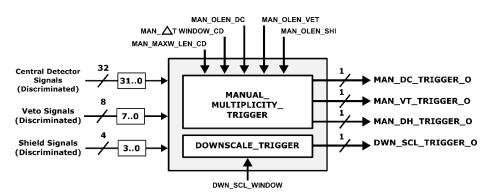

| Figura 46 - Diagrama de arquitetura do trigger manual                                 | 50     |

| Figura 47 - Comportamento de eventos de trigger com vetos                             | 52     |

| Figura 48 - Identificador e contador de eventos.                                      | 53     |

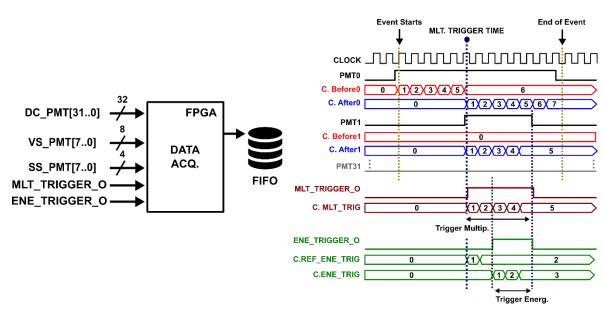

| Figura 49 - Funcionamento do sistema de aquisição de dados                            | 54     |

| Figura 50 - Diagrama de reconstituição dos dados adquiridos                           | 55     |

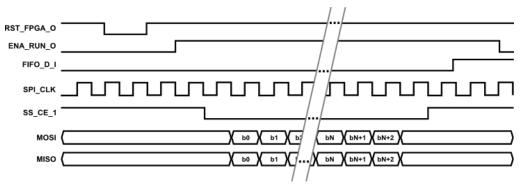

| Figura 51 - Sinais de comunicação FPGA - SBC.                                         | 56     |

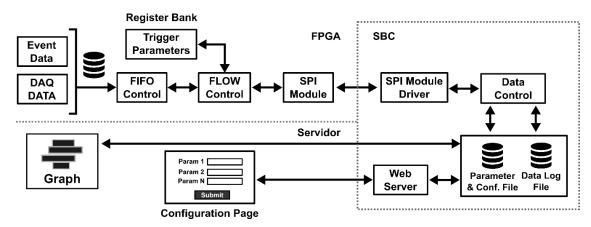

| Figura 52 - Fluxo de configuração e comunicação de dados                              | 57     |

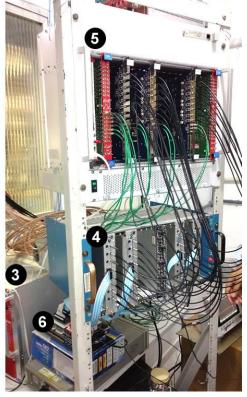

| Figura 53 - Configuração do Experimento no Laboratório do CBPF                        | 59     |

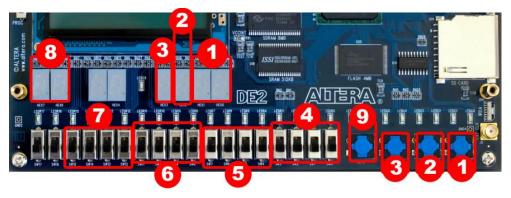

| Figura 54 - FPGA e SBC utilizadas no experimento de trigger                           | 60     |

| Figura 55 - Função de aproximação de 0 a 285 ns com passo de 1 ns                     | 62     |

| Figura 56 - Resultado da normalização dos dados com passo de 5 ns                     | 62     |

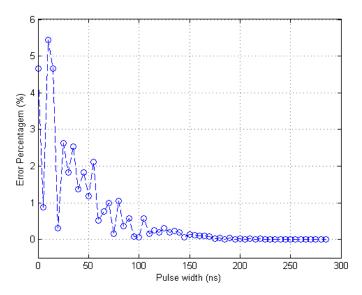

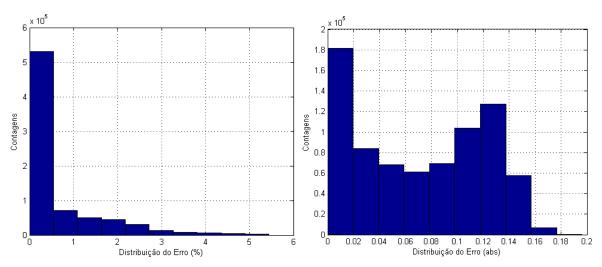

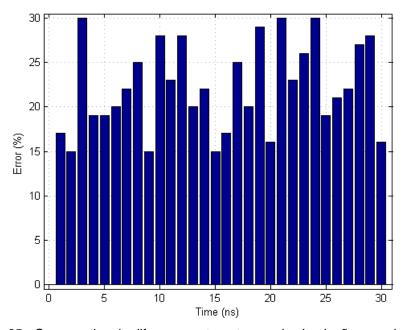

| Figura 57 - Erros da aproximação em ponto fixo (percentual)                           | 63     |

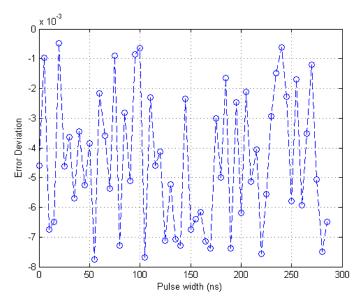

| Figura 58 - Erro de aproximação em ponto fixo (absoluto)                              | 63     |

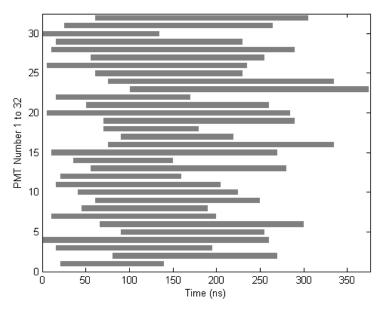

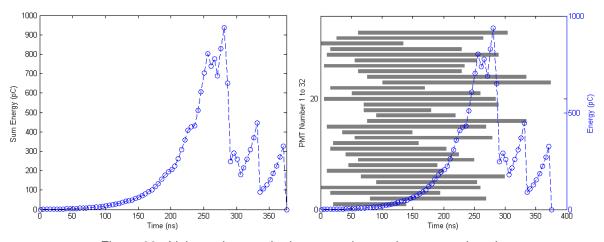

| Figura 59 - Exemplo de evento de neutrinos do <i>testbench</i> de energia             | 64     |

| Figura 60 - Valores de energia do evento de neutrinos no testbench                    | 64     |

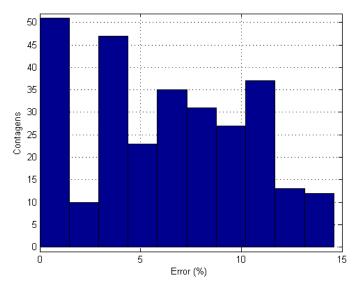

| Figura 61 - Histograma de do erro acumulado a partir do test bench                    | 65     |

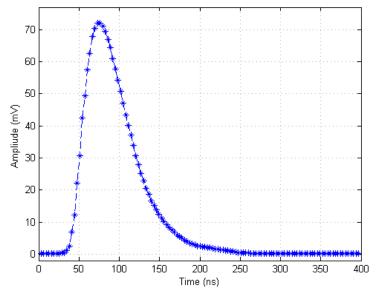

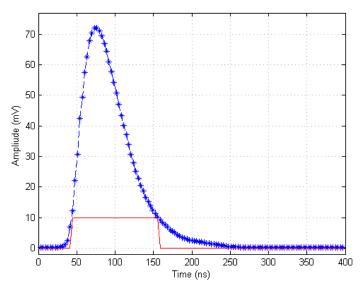

| Figura 62 - Sinal de neutrino gerado por simulação.                                   | 66     |

| Figura 63 - Aplicação do <i>threshold</i> analógico de 10 mV nos sinais dos neutrinos | 67     |

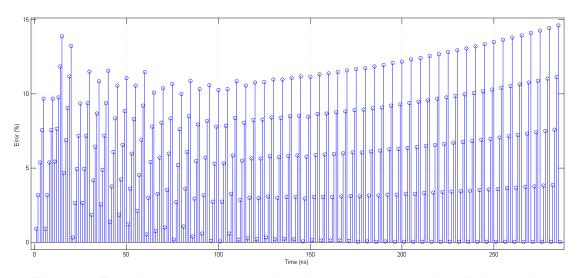

| Figura 64 - Erros de truncamento causados pela amostragem na estimação da energ       | gia.67 |

| Figura 65 - Histograma do erro causado pela amostragem na estimação da energia.       | 68     |

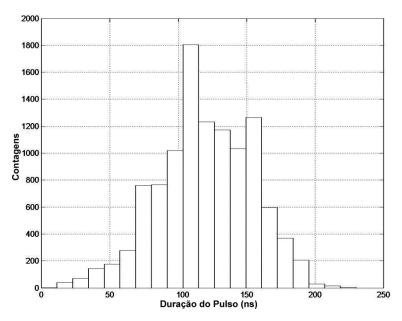

| Figura 66 - Histograma da duração dos sinais de 10976 eventos                         | 69     |

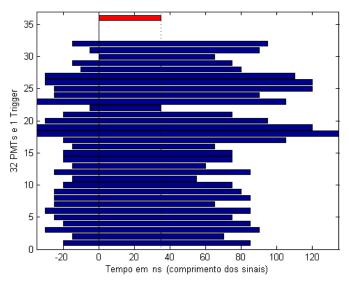

| Figura 67 - Um evento de trigger com threshold igual a 32.                            | 70     |

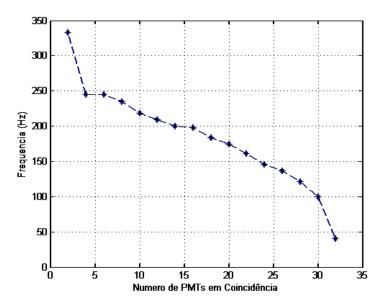

| Figura 68 - Frequência de eventos para diferentes threshold de PMTs                   | 70     |

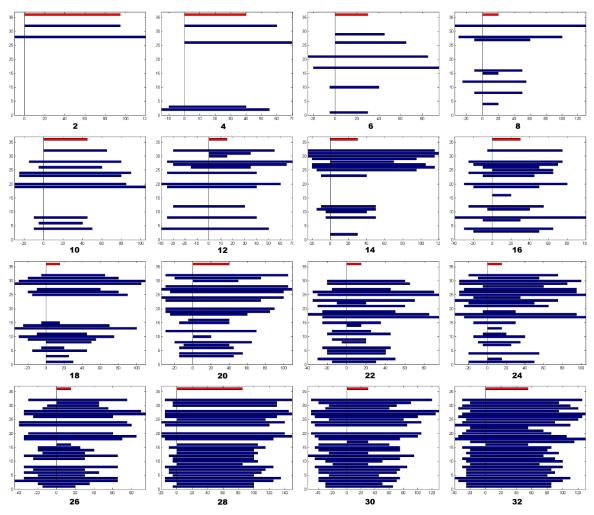

| Figura 69 - Evento de trigger com threshold igual a 18.                               | 71     |

| Figura 70 - Resultados de aquisição para diferentes thresholds de multiplicidade      | 71     |

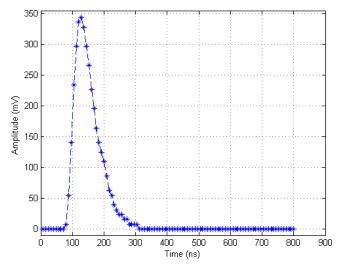

| Figura 71 - Sinal do PMT 0 amostrado pelo NDAQ                                   | 72 |

|----------------------------------------------------------------------------------|----|

| Figura 72 - Amostra do NDAQ discriminada                                         | 73 |

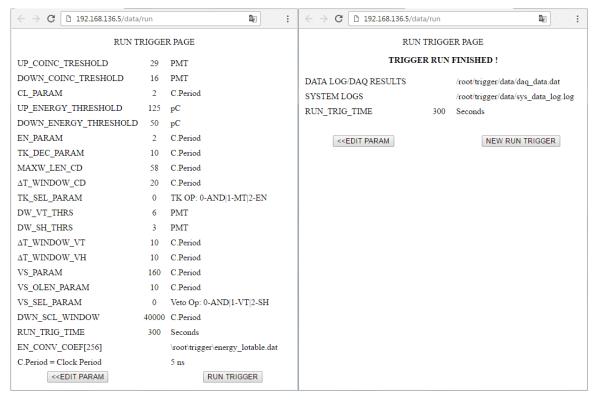

| Figura 73 - Tela de configuração de parâmetros via SBC                           | 74 |

| Figura 74 - Tela para execução das rodadas de <i>trigger</i>                     | 75 |

| Figura 75 - Fotografia dos componentes do FPGA utilizados na configuração manual | 76 |

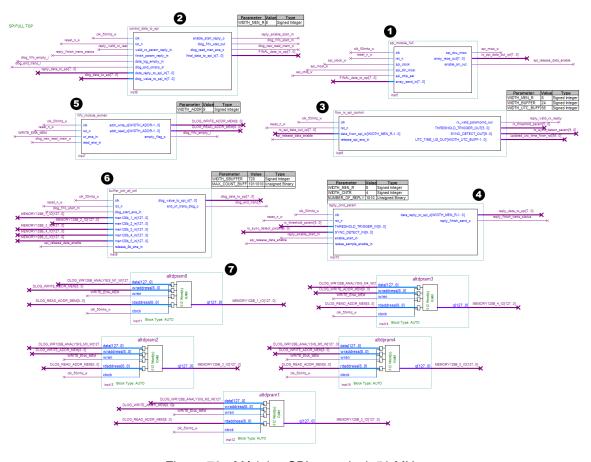

| Figura 76 - Módulos SPI com clock 50 MHz                                         | 77 |

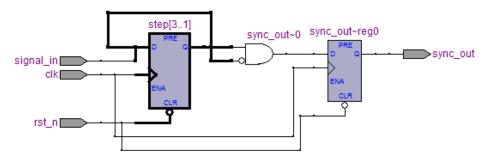

| Figura 77 - Circuito de <i>edge detection</i> .                                  | 79 |

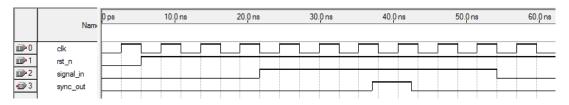

| Figura 78 - Diagrama de onda dos sinais do edge detection                        | 79 |

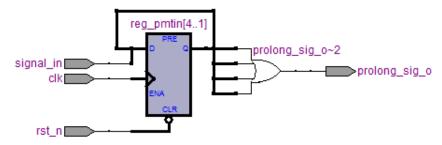

| Figura 79 - Circuito de prolongamento de sinal                                   | 79 |

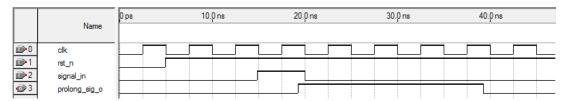

| Figura 80 - Diagrama de onda dos sinais do circuito de prolongamento de sinal    | 80 |

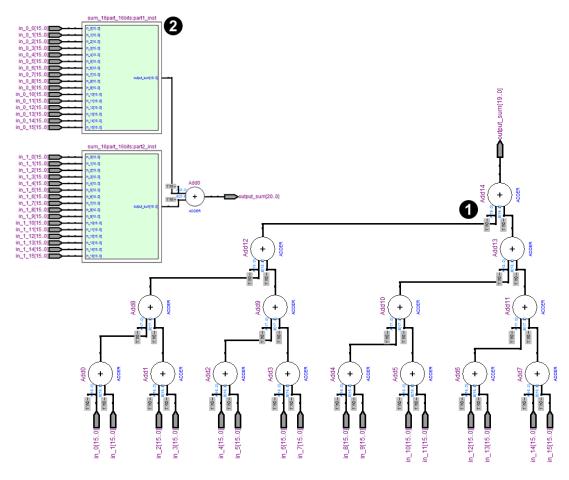

| Figura 81 - RTL View do somador de energia                                       | 80 |

| Figura 82 - Circuito do trigger por energia no Altera Quartus II                 | 81 |

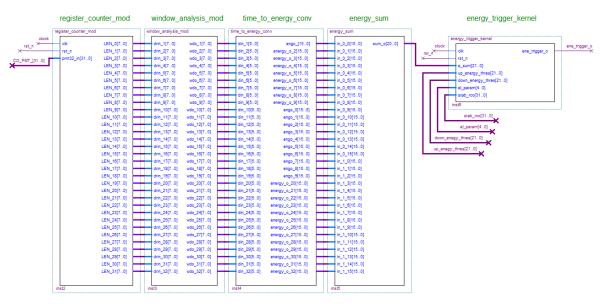

| Figura 83 - Teste experimental de tempos de resposta                             | 82 |

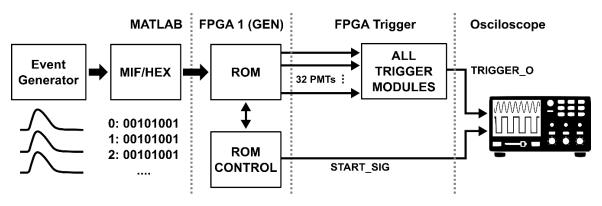

| Figura 84 - Histograma de tempos de resposta de trigger via testbench            | 83 |

| Figura 85 - Comparativo da diferença entre o tempo de simulação e o adquirido    | 83 |

## **LISTA DE TABELAS**

| Tabela 1 - Pico de amplitude média do front-end e SNR para resposta de SPE     | 28 |

|--------------------------------------------------------------------------------|----|

| Tabela 2 - Parametros de aproximação linear (Ax + B)                           | 28 |

| Tabela 3 - Parâmetros de aproximação da função f(x) = Ax <sup>B</sup> + C [29] | 29 |

| Tabela 4 - Principais parâmetros de configuração e comunicação                 | 57 |

| Tabela 5 - Comparativo entre dados do NDAQ e do sistema de aquisição FPGA      | 73 |

## LISTA DE ABREVIATURAS E SÍMBOLOS

ADC Analog to Digital Converter

AF Attenuation Factors

AGS Alternating Gradient Synchrotron

AMT ATLAS Muon TDC

ASIC Application-Specific Integrated Circuit

BTB Borexino Trigger Board

c Velocidade da luz

CBPF Centro Brasileiro de Pesquisas Físicas

CERN Conseil Européen pour la Recherche Nucléaire

DAQ Data Acquisition Systems

DSP Digital Signal Processing

DUV Design Under Verification

FADC Flash Analog-to-Digital Converter

FEE Front-end Electronics

FIFO First In First Out

FPGA Field Programmable Gate Array

FWHW Full-Width Half-Maximum

GDSII Graphic Database System Information Interchange

HDL Hardware Description Language

HEP High Energy Physics

HV High Voltage

12C Inter-Integrated Circuit

UFJF Universidade Federal de Juiz de Fora

IP Intellectual Property

ISS Input Status Synchronization

KAMLAND Kamioka Liquid Scintillator Antineutrino Detector

L1 Level 1

LEP Large Electron-Positron

LHC Large Hadron Collider

LUT Look Up Table

Me Massa do elétron

MIF Memory Initialization File

Mn Massa do novo núcleo

Mo Massa do núcleo original

MTB Muon Trigger Board

NDAQ Neutrinos Data Acquisition

PC Pico Coulomb

PLL Phase-locked loop

PMT Photomultiplier Tubes

QBEE QTC-Based Electronics with Ethernet

QTC Charge-to-time Converter

RENO Reactor Experiment for Neutrino Oscillation

ROM Read Only Memory

RTL Register-Transfer Level

SBC Single Board Computer

SNEWS SuperNova Early Warning System

SNR Signal-to-Noise Ratio

SPE Single Photo Electron

SPI Serial Parallel Interface

SUPER-K Super-Kamiokande

TB Trigger Board

TCP/IP Transmission Control Protocol/Internet Protocol

TDC Time-to-digital Converter

TMB Trigger Master Board

TTW Trigger Time Window

UFABC Universidade Federal do ABC

UFBA Universidade Federal da Bahia

UNICAMP Universidade Estadual de Campinas

USB Universal Serial Bus

UVM Universal Verification Methodology

VCD Value Change Dump

VME Versa Module Europa bus

VPN Virtual Private Network

WWW World-Wide Web

## SUMÁRIO

| R  | ESU   | MO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VI    |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ΑI | 3STF  | RACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . VII |

| LI | STA   | DE FIGURAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VIII  |

| LI | STA   | DE TABELAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | XI    |

| LI | STA   | DE ABREVIATURAS E SÍMBOLOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . XII |

| 1  | Intro | odução                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1     |

|    | 1.1   | Apresentação do Problema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2     |

|    | 1.2   | Objetivos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3     |

|    | 1.3   | Organização do Documento                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3     |

| 2  | Intro | odução à Física de Altas Energias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5     |

|    | 2.1   | Neutrinos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5     |

|    | 2.2   | Detectores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7     |

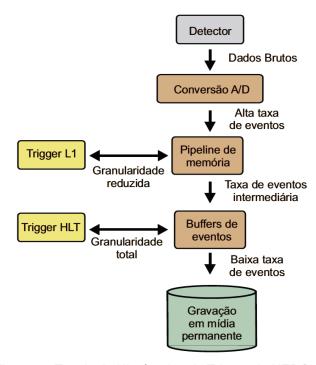

| 3  | Sel   | eção online de Eventos em Detectores de Neutrinos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12    |

|    | 3.1   | Super-Kamiokande                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13    |

|    | 3.2   | Double Chooz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15    |

|    | 3.3   | Daya Bay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18    |

|    | 3.4   | Borexino                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19    |

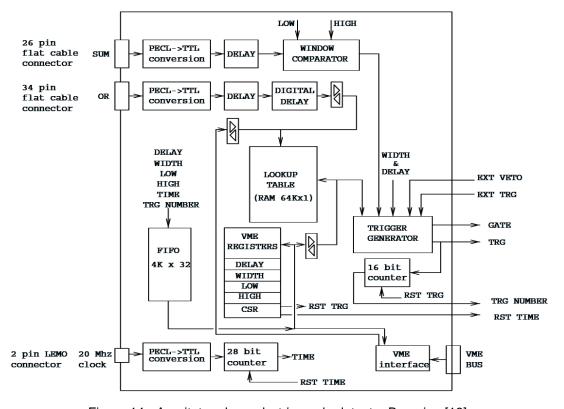

|    | 3.5   | RENO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20    |

| 4  | 0 0   | Detector Neutrinos Angra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22    |

|    | 4.1   | Caracterização dos PMTs e Front-End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27    |

| 5  | Met   | todologias de Projeto de Circuitos Digitais                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30    |

|    | 5.1   | Fluxo de Implementação                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30    |

|    | 5.2   | Sistemas de Verificação Funcional e Testes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32    |

| 6  |       | posta de Sistemas de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Sistemas de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Sistemas de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Sistemas de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Sistemas de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Sistemas de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Seleção <i>Online</i> de Eventos de Antineutrinos do Experimenta de Seleção de Antineutrinos do Experimenta de Seleção de Se |       |

|    | 6.1   | Requisitos dos Sistemas de <i>Trigger</i> de Primeiro Nível                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37    |

|    | 6.2   | Arquitetura Detalhada dos Sistemas de Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39    |

|    | 6.3   | Trigger de Antineutrinos por Multiplicidade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41    |

|    | 6.4   | Trigger de Antineutrinos por Energia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44    |